'Why is it wrong when I separately assign the output values?

The following code is correct and successfully complied.

module top_module (

input [4:0] a, b, c, d, e, f,

output [7:0] w, x, y, z );//

assign {w,x,y,z} = {a,b,c,d,e,f,2'b11};

endmodule

The next is wrong, which is confusing.

module top_module (

input [4:0] a, b, c, d, e, f,

output [7:0] w, x, y, z );//

assign w = {a,b[2:0]};

assign x = {c[4:3],b[2:0]};

assign y = {c[4:3],d[2:0]};

assign z = {d[4:3],2'b11};

endmodule

Why is it wrong when I separately assign the output values?

By the way, here's the original problem:

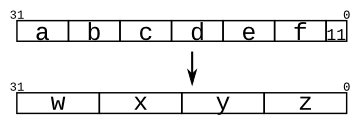

Given several input vectors, concatenate them together then split them up into several output vectors. There are six 5-bit input vectors: a, b, c, d, e, and f, for a total of 30 bits of input. There are four 8-bit output vectors: w, x, y, and z, for 32 bits of output. The output should be a concatenation of the input vectors followed by two 1 bits:

I've tried so many times, and I just can't assign values to them separately.

Solution 1:[1]

You need to be a little more careful when counting the number of bits in each assignment. You need to make sure the RHS of each has 8 bits. And, you need to use the proper part-selects of each input. Your code does not even use 2 of the inputs: e and f.

This is equivalent to your 1st code example:

module top_module (

input [4:0] a, b, c, d, e, f,

output [7:0] w, x, y, z );//

assign w = {a[4:0], b[4:2] };

assign x = {b[1:0], c[4:0], d[4] };

assign y = {d[3:0], e[4:1] };

assign z = {e[0] , f[4:0], 2'b11};

endmodule

It is not necessary to use [4:0], but I chose to do so to make it more obvious how many bits are on the RHS.

Sources

This article follows the attribution requirements of Stack Overflow and is licensed under CC BY-SA 3.0.

Source: Stack Overflow

| Solution | Source |

|---|---|

| Solution 1 |